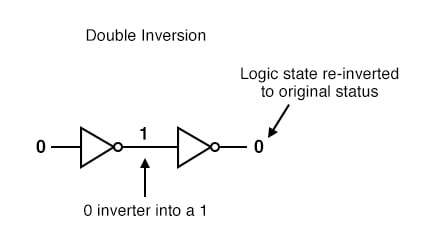

Pokud bychom měli připojit dva střídače brány dohromady tak, že výstup jednoho přivádí do vstupu dalšího, dvě inverze funkce by „zrušit“ navzájem tak, že tam by byla žádná inverze od vstupu k výstupu:

i Když to může zdát jako zbytečná věc, že to má praktické uplatnění. Nezapomeňte, že hradlové obvody jsou zesilovače signálu, bez ohledu na to, jakou logickou funkci mohou vykonávat.

slabý zdroj signálu (ten, který není schopen získávání nebo potopení velmi mnoho proudu do zátěže), může být posílen pomocí dvou invertorů, jako dvojice je znázorněno na předchozí ilustraci. Úroveň logiky se nemění, ale v případě potřeby jsou k dispozici plné možnosti získávání proudu nebo potopení konečného střídače pro řízení odporu zátěže.

pro tento účel je vytvořena speciální logická brána zvaná vyrovnávací paměť, která plní stejnou funkci jako dva střídače. Jeho symbolem je jednoduše trojúhelník, bez invertující „bubliny“ na výstupním terminálu:

Vyrovnávací paměť v Obvodu s Open-Collector Výstup

vnitřní schéma pro typický open-kolektoru vyrovnávací paměti je příliš neliší od toho jednoduchého měniče: pouze jeden common-emitor tranzistoru fázi je přidán do re-inverze výstupního signálu.

„High“ Vstupní Analýza,

Pojďme analyzovat tento obvod na dvě podmínky: vstupní logická úroveň “ 1 „a vstupní logická úroveň“ 0.“První, „high“ (1) vstup:

stejně Jako předtím s střídače obvodu, „high“ vstupu způsobí žádné vedení přes levé řízení dioda Q1 (emitor-báze PN přechodu). Všechny R1 je proud prochází báze tranzistoru Q2, nasycení je:

S Q2 nasycené příčiny Q3 být nasycené, stejně, což vede k velmi málo kleslo napětí mezi základnou a emitor výstupu tranzistoru Q4. Q4 tedy bude v mezním režimu a nebude provádět žádný proud.

výstupní terminál bude plovoucí (ani připojený k zemi ani Vcc), což bude ekvivalentní „vysokému“ stavu na vstupu další brány TTL, do které se tato přivádí. „Vysoký“ vstup tedy poskytuje“ vysoký “ výstup.

„Nízká“ Vstupní Analýza,

S „nízkými“ input signal (vstupní terminál uzemněn), analýza vypadá něco jako toto:

R1 je aktuální je nyní přesměrován přes vstupní spínač, čímž se eliminuje základní proud Q2. To nutí tranzistor Q2 do mezní hodnoty, takže žádný základní proud neprochází ani Q3.

S Q3 cutoff stejně, Q4 je nasycený proud přes rezistor R4, tedy připojení výstupního terminálu k zemi, což je „nízké“ logické úrovni. „Nízký“ vstup tedy poskytuje“ nízký “ výstup.

Schéma s Totem Výstupní Tranzistory

schéma pro vyrovnávací paměť obvodu s totem výstupní tranzistory je trochu složitější, ale základní principy, a rozhodně pravdu stolu, jsou stejné jako pro open-collector obvodu:

RECENZE:

- Dva střídače, nebo NE, brány připojen v „sérii“ tak, aby se klenby, pak re-invertovat binární bit plnit funkci vyrovnávací paměti. Vyrovnávací paměti brány pouze slouží k zesílení signálu: užívání „slabý“ zdroj signálu, který není schopen získávání nebo potopení moc aktuální, a posílení stávající kapacity signálu tak, aby byl schopen řídit zatížení.

- vyrovnávací obvody jsou symbolizovány trojúhelníkovým symbolem bez invertorové bubliny.“

- Vyrovnávací paměti, jako invertory, mohou být provedeny v open-collector výstup nebo totem výstupní formy.