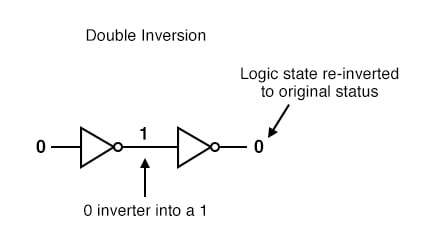

hvis vi skulle forbinde to inverterporte sammen, så output fra en, der føres ind i input fra en anden, ville de to inversionsfunktioner “annullere” hinanden, så der ikke ville være nogen inversion fra input til endelig output:

selvom dette kan virke som en meningsløs ting at gøre, det har praktisk anvendelse. Husk, at gate kredsløb er signalforstærkere, uanset hvilken logisk funktion de kan udføre.

en svag signalkilde (en, der ikke er i stand til at købe eller synke meget strøm til en belastning) kan forstærkes ved hjælp af to omformere som parret vist i den foregående illustration. Logikniveauet er uændret, men den fulde strøm-sourcing eller synkefunktioner i den endelige inverter er tilgængelige for at drive en belastningsmodstand, hvis det er nødvendigt.

til dette formål fremstilles en speciel logikport kaldet en buffer til at udføre den samme funktion som to omformere. Dens symbol er simpelthen en trekant uden omvendt “boble” på udgangsterminalen:

Bufferkredsløb med Open-Collector Output

det interne skematiske diagram for en typisk Open-collector buffer er ikke meget forskellig fra en simpel inverter: kun et mere almindeligt emitter transistortrin tilføjes for at invertere udgangssignalet igen.

“High” Input analyse

lad os analysere dette kredsløb for to betingelser: et inputlogikniveau på “1 “og et inputlogikniveau på” 0.”Først en” høj”(1) indgang:

som før med inverterkredsløbet forårsager den” høje ” indgang ingen ledning gennem den venstre styrediode i 1.kvartal (emitter-til-base PN-kryds). Al R1S strøm går gennem basen af transistor 2. kvartal og mætter den:

at have 2.kvartal mættet forårsager også, at 3. kvartal er mættet, hvilket resulterer i, at meget lidt spænding faldt mellem basen og emitteren af den endelige udgangstransistor 4. kvartal. Således vil 4. kvartal være i cutoff-tilstand uden strøm.

outputterminalen flyder (hverken forbundet til jorden eller Vcc), og dette svarer til en “høj” tilstand på indgangen til den næste TTL-port, som denne føder ind til. Således giver en” høj “indgang en” høj ” udgang.

” lav ” Indgangsanalyse

Med et “lavt” indgangssignal (indgangsterminal jordet) ser analysen sådan ud:

al R1S strøm omdirigeres nu gennem indgangskontakten, hvilket eliminerer basisstrøm gennem 2.kvartal. Dette tvinger transistor 2. kvartal til cutoff, så der heller ikke går nogen basestrøm gennem 3.kvartal.

med 3. kvartal cutoff vil 4. kvartal også blive mættet af strømmen gennem modstand R4 og dermed forbinde udgangsterminalen til jorden, hvilket gør det til et “lavt” logikniveau. Således giver en” lav “indgang en” lav ” udgang.

skematisk Diagram med Totempol Output transistorer

det skematiske diagram for et bufferkredsløb med totempol output transistorer er lidt mere komplekst, men de grundlæggende principper, og bestemt sandhedstabellen, er de samme som for det åbne kollektor kredsløb:

anmeldelse:

- to inverter, eller ej, porte forbundet i “serie” for at invertere, derefter re-invertere, en binær bit udføre funktionen af en buffer. Bufferporte tjener kun formålet med signalforstærkning: at tage en “svag” signalkilde, der ikke er i stand til at købe eller synke meget strøm, og øge signalets aktuelle kapacitet for at kunne køre en belastning.

- Bufferkredsløb er symboliseret med et trekantsymbol uden inverter “boble.”

- buffere, som omformere, kan fremstilles i Open-collector output eller totempole output former.