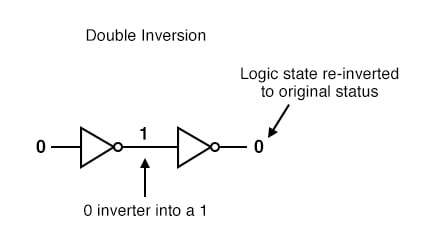

Se dovessimo collegare due inverter cancelli insieme in modo che l’output di un sistema alimentato con l’ingresso di un altro, i due inversione di funzioni “annulla” a vicenda, in modo che non ci sarebbe alcuna inversione di input / output finale:

Mentre questo può sembrare una cosa inutile da fare, non hanno applicazione pratica. Ricorda che i circuiti gate sono amplificatori di segnale, indipendentemente dalla funzione logica che possono svolgere.

Una sorgente di segnale debole (una che non è in grado di sourcing o affondare molta corrente ad un carico) può essere potenziato per mezzo di due inverter come la coppia mostrato nella figura precedente. Il livello logico è invariato, ma sono disponibili le capacità complete di approvvigionamento di corrente o di affondamento dell’inverter finale per pilotare una resistenza di carico, se necessario.

A questo scopo, viene prodotto uno speciale gate logico chiamato buffer per eseguire la stessa funzione di due inverter. Il suo simbolo è semplicemente un triangolo, senza inversione “bolla” sul terminale di uscita:

Buffer Circuito con Uscita Open-Collector

L’interno schema di un tipico open-collector buffer non è molto diverso da quello di un semplice inverter: solo un altro comune-emettitore del transistor è aggiunto invertire il segnale di uscita.

Analisi di ingresso”alto”

Analizziamo questo circuito per due condizioni: un livello logico di ingresso di “1” e un livello logico di ingresso di ” 0.”In primo luogo, un ingresso” alto”(1):

Come prima con il circuito inverter, l’ingresso” alto ” non causa alcuna conduzione attraverso il diodo di sterzo sinistro di Q1 (giunzione PN emettitore-base). Tutta la corrente di R1 passa attraverso la base del transistor Q2, saturandolo:

Avere Q2 saturo fa sì che anche Q3 sia saturo, con conseguente minima caduta di tensione tra la base e l’emettitore del transistor di uscita finale Q4. Pertanto, Q4 sarà in modalità di taglio, senza condurre corrente.

Il terminale di uscita sarà fluttuante (né collegato a terra né Vcc), e questo sarà equivalente a uno stato “alto” sull’ingresso del prossimo gate TTL a cui questo si alimenta. Pertanto, un ingresso “alto” fornisce un’uscita “alta”.

Analisi di ingresso”basso”

Con un segnale di ingresso “basso” (terminale di ingresso collegato a terra), l’analisi è simile a questa:

Tutta la corrente di R1 viene ora deviata attraverso l’interruttore di ingresso, eliminando così la corrente di base attraverso Q2. Questo costringe transistor Q2 in taglio in modo che nessuna corrente di base passa attraverso Q3 sia.

Con Q3 cutoff pure, Q4 è sarà saturo dalla corrente attraverso resistenza R4, collegando così il terminale di uscita a terra, che lo rende un “basso” livello logico. Pertanto, un ingresso “basso” fornisce un’uscita “bassa”.

Diagramma schematico con transistor di uscita Totem Pole

Il diagramma schematico per un circuito buffer con transistor di uscita totem pole è un po ‘ più complesso, ma i principi di base, e certamente la tabella di verità, sono gli stessi del circuito open-collector:

RECENSIONE:

- Due inverter, o NO, porte collegate in “serie” in modo da invertire, poi ri-invertire, un bit binario svolgere la funzione di un buffer. Le porte buffer servono semplicemente allo scopo di amplificare il segnale: prendere una sorgente di segnale “debole” che non è in grado di procurarsi o affondare molta corrente e aumentare la capacità di corrente del segnale in modo da essere in grado di pilotare un carico.

- I circuiti tampone sono simboleggiati da un simbolo triangolare senza bolla “inverter”.”

- I buffer, come gli inverter, possono essere realizzati in moduli di uscita a collettore aperto o totem.