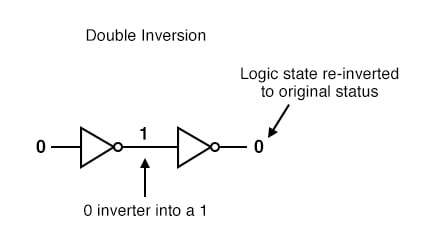

als we twee inverterpoorten met elkaar zouden verbinden zodat de uitvoer van de ene naar de invoer van de andere wordt ingevoerd, zouden de twee inversiefuncties elkaar “opheffen” zodat er geen inversie van input naar uiteindelijke uitvoer zou zijn:

terwijl dit misschien zinloos lijkt te doen, het heeft praktische toepassing. Vergeet niet dat poortcircuits signaalversterkers zijn, ongeacht welke logische functie ze kunnen uitvoeren.

een zwakke signaalbron (een die niet in staat is om zeer veel stroom tot een belasting te sourcen of te laten zinken) kan worden versterkt door middel van twee omvormers zoals het paar in de vorige afbeelding. Het logische niveau is ongewijzigd, maar de volledige stroom-sourcing of zinkmogelijkheden van de uiteindelijke omvormer zijn beschikbaar om een belastingsweerstand aan te drijven indien nodig.

voor dit doel wordt een speciale logische poort, een buffer genaamd, gefabriceerd om dezelfde functie uit te voeren als twee inverters. Het symbool is gewoon een driehoek, zonder omgekeerde “bubble” op de uitgang terminal:

Buffercircuit met Open-Collectoruitgang

het interne schema voor een typische open-collectorbuffer verschilt niet veel van dat van een eenvoudige inverter: er wordt slechts één meer gebruikelijke transistortrap van de emitter toegevoegd om het uitgangssignaal opnieuw om te keren.

“High” Input Analysis

laten we dit circuit analyseren voor twee voorwaarden: een invoerlogiceniveau van ” 1 “en een invoerlogiceniveau van “0”.”First, a” high”(1) input:

zoals voorheen bij het invertercircuit veroorzaakt de” high ” input geen geleiding door de linker stuurdiode van Q1 (emitter-to-base PN junction). Alle stroom van R1 gaat door de basis van de transistor Q2 en verzadigt deze:

met verzadigde Q2 zorgt ervoor dat ook Q3 verzadigd is, wat resulteert in een zeer geringe daling van de spanning tussen de basis en de zender van de uiteindelijke uitgangstransistor Q4. Dus, Q4 zal in cutoff-modus, het uitvoeren van geen stroom.

De uitvoerterminal zal zwevend zijn (noch verbonden met de grond noch met Vcc), en dit zal gelijk zijn aan een “hoge” status op de ingang van de volgende TTL poort die deze invoert. Een “hoge” input geeft dus een” hoge ” output.

“Low” Input Analysis

met een “low” input signal (input terminal geaard) ziet de analyse er ongeveer zo uit:

alle stroom van R1 wordt nu omgeleid door de input switch, waardoor de basisstroom door Q2 wordt geëlimineerd. Dit dwingt transistor Q2 in cutoff zodat er ook geen basisstroom door Q3 gaat.

met Q3 cutoff zal ook Q4 verzadigd worden door de stroom via weerstand R4, waardoor de uitgang terminal wordt verbonden met de grond, waardoor het een “laag” logisch niveau is. Dus, een” lage “input geeft een “lage” output.

schematisch Diagram met Totempole-Uitgangstransistors

het schematische diagram voor een buffercircuit met totempole-uitgangstransistors is iets complexer, maar de basisprincipes, en zeker de waarheidstabel, zijn hetzelfde als voor het open-collectorcircuit:

recensie:

- twee inverter-poorten die in” series ” zijn verbonden om een binaire bit inverteren en dan opnieuw inverteren en de functie van een buffer uitvoeren. Buffer poorten dienen alleen maar het doel van signaalversterking: het nemen van een” zwakke ” signaalbron die niet in staat is om sourcing of zinken veel stroom, en het stimuleren van de huidige capaciteit van het signaal om te kunnen rijden een belasting.

- Buffercircuits worden gesymboliseerd door een driehoek symbool zonder inverter “bubble.”

- Buffers, zoals inverters, kunnen worden gemaakt in open-collector output of totem pole output vormen.