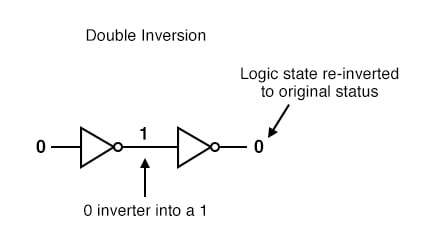

gdybyśmy połączyli ze sobą dwie bramki falownika, aby wyjście jednej z nich było podawane na wejście drugiej, dwie funkcje inwersyjne „anulowałyby” się nawzajem, aby nie było inwersji z wejścia na końcowe wyjście:

chociaż może to wydawać się bezsensowne rzecz do zrobienia, ma praktyczne zastosowanie. Pamiętaj, że obwody bramkowe są wzmacniaczami sygnału, niezależnie od tego, jaką funkcję logiczną mogą pełnić.

słabe źródło sygnału (takie, które nie jest w stanie pozyskiwać lub tonąć bardzo dużo prądu do obciążenia) może być wzmocnione za pomocą dwóch falowników, takich jak para pokazana na poprzedniej ilustracji. Poziom logiki pozostaje niezmieniony, ale dostępne są pełne możliwości pozyskiwania lub tonienia prądu końcowego falownika, aby w razie potrzeby napędzać opór obciążenia.

w tym celu produkowana jest specjalna bramka logiczna zwana buforem, która pełni tę samą funkcję co dwa falowniki. Jego symbolem jest po prostu Trójkąt, bez odwróconej „bańki” na terminalu wyjściowym:

Obwód buforowy z wyjściem otwartego kolektora

wewnętrzny schemat typowego bufora otwartego kolektora nie różni się zbytnio od zwykłego falownika: dodano tylko jeden typowy stopień tranzystora emitera, aby ponownie odwrócić sygnał wyjściowy.

Analiza wejścia”High”

przeanalizujmy ten obwód pod kątem dwóch warunków: poziom logiki wejściowej ” 1 „i poziom logiki wejściowej” 0.”Po pierwsze, wejście” high”(1):

jak poprzednio w obwodzie falownika, wejście” high ” nie powoduje przewodzenia przez lewą diodę sterującą Q1 (złącze emiter-baza PN). Cały prąd R1 przechodzi przez bazę tranzystora Q2, nasycając go:

nasycenie Q3 powoduje również nasycenie Q3, co skutkuje bardzo niewielkim spadkiem napięcia między bazą a emiterem końcowego tranzystora wyjściowego Q4. W ten sposób Q4 będzie w trybie odcięcia, nie przewodząc prądu.

terminal wyjściowy będzie pływający (ani podłączony do masy, ani do Vcc), a to będzie równoznaczne ze stanem „wysokim” na wejściu następnej bramki TTL, do której ta podaje. Tak więc wejście ” wysokie „daje” wysokie ” wyjście.

„niska” Analiza wejściowa

przy „niskim” sygnale wejściowym (uziemiony terminal wejściowy), analiza wygląda mniej więcej tak:

cały prąd R1 jest teraz kierowany przez przełącznik wejściowy, eliminując w ten sposób prąd bazowy przez Q2. To zmusza tranzystor Q2 do odcięcia tak, że żaden prąd bazowy nie przechodzi przez Q3.

z odcięciem Q3, Q4 jest nasycony prądem przez rezystor R4, łącząc w ten sposób terminal wyjściowy z masą, co czyni go „niskim” poziomem logicznym. Tak więc wejście ” low „daje wyjście” low”.

schemat z tranzystorami biegunowymi totemu

schemat dla obwodu buforowego z tranzystorami biegunowymi totemu jest nieco bardziej złożony, ale podstawowe zasady, a na pewno tablica prawdy, są takie same jak dla obwodu otwartego kolektora:

recenzja:

- dwa falowniki, lub nie, bramki połączone w „szereg” tak, aby odwrócić, a następnie ponownie odwrócić, bit binarny pełni funkcję bufora. Bramki buforowe służą jedynie wzmocnieniu sygnału: pobieraniu „słabego” źródła sygnału, które nie jest w stanie pozyskiwać lub tonąć dużo prądu, i zwiększaniu pojemności prądowej sygnału, aby móc napędzać obciążenie.

- obwody buforowe symbolizowane są symbolem trójkąta bez falownika „bąbel”.”

- bufory, podobnie jak falowniki, mogą być wykonane w postaci wyjścia z otwartym kolektorem lub wyjścia z biegunem totemowym.